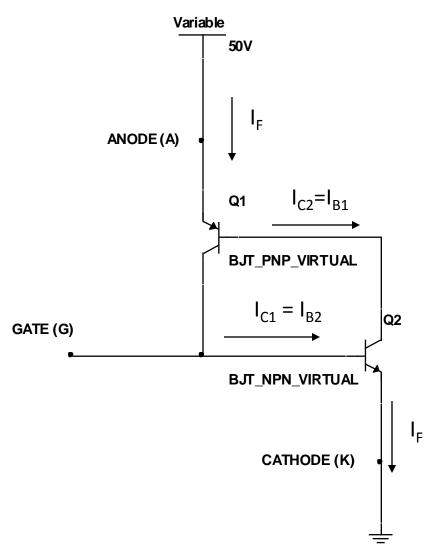

### **Apply Biasing**

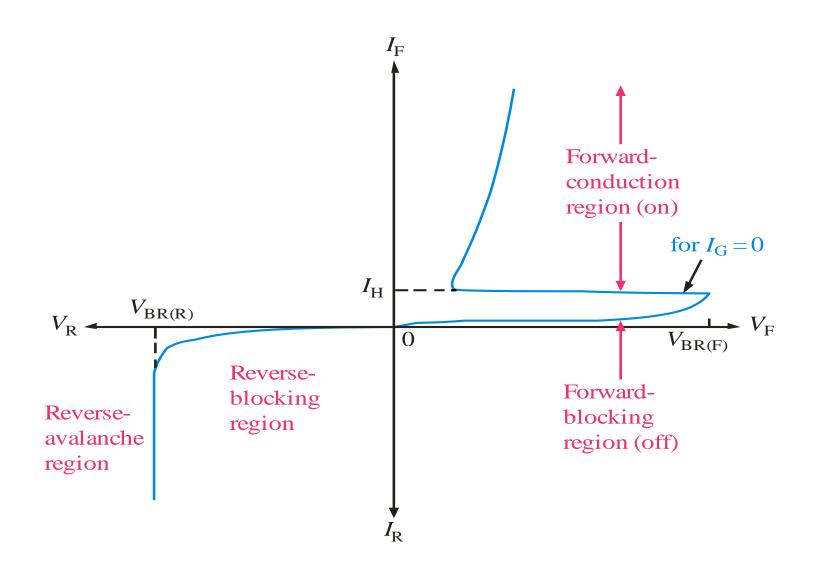

With the Gate terminal OPEN, both transistors are OFF. As the applied voltage increases, there will be a "breakdown" that causes both transistors to conduct (saturate) making  $I_F > 0$  and  $V_{AK} = 0$ .

$$V_{Breakdown} = V_{BR(F)}$$

## Static I-V Characteristics of SCR

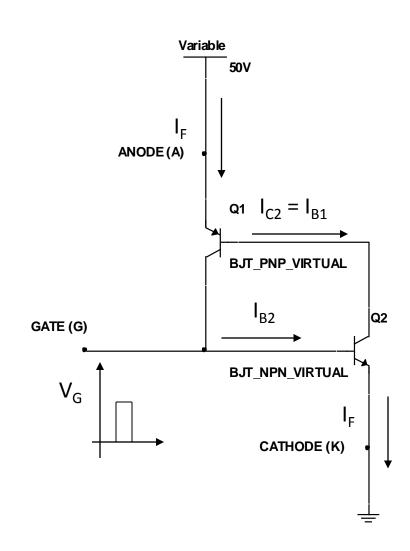

#### Apply a Gate Current

For  $0 < V_{AK} < V_{BR(F)}$ ,

Turn Q<sub>2</sub> ON by applying a current into the Gate

This causes Q<sub>1</sub> to turn ON, and eventually both transistors SATURATE

$$V_{AK} = V_{CEsat} + V_{BEsat}$$

If the Gate pulse is removed, Q<sub>1</sub> and Q<sub>2</sub> still stay ON!

# Latching & Holding Current

### Latching current

Minimum anode current that must flow through the SCR in order for it to stay on initially after gate signal is removed.

### **Holding Current**

Minimum value of anode current, required to maintain SCR in conducting state.